# Impact of different compiler options on energy consumption

James Pallister

University of Bristol / Embecosm

Simon Hollis

University of Bristol

Jeremy Bennett Embecosm

#### Motivation

- Compiler optimizations are claimed to have a large impact on software:

- Performance

- Energy

- No extensive study prior to this considering:

- Different benchmarks

- Many individual optimizations

- Different platforms

- This work looks at the effect of many different optimizations across 10 benchmarks and 5 platforms.

- 238 Optimization passes covered by 150 flags

- Huge amount of combinations

#### This Talk

- This talk will cover:

- Importance of benchmarks

- How to explore 2^150 combinations of options

- Demo

- Correlation between time and energy

- How to predict the effect of the optimizations

- The best optimizations

# Importance of Benchmarks

- One benchmark can't trigger all optimizations

- Perform differently on different platforms

- Need a range of benchmarks

- Broad categories to be considered for a benchmark:

- Integer

- Floating point

- Branching

- Memory

# Our Benchmark List

| Name              | Source  | В            | M            | Ι        | FP           | ${ m T}$ | License                   | Category             |

|-------------------|---------|--------------|--------------|----------|--------------|----------|---------------------------|----------------------|

| Blowfish          | MiBench | L            | Μ            | Н        | L            | Multi    | GPL                       | security             |

| CRC32             | MiBench | M            | ${ m L}$     | Η        | ${ m L}$     | Single   | $\operatorname{GPL}$      | network, telecomm    |

| Cubic root solver | MiBench | ${\rm L}$    | M            | Η        | ${ m L}$     | Single   | $\operatorname{GPL}$      | automotive           |

| Dijkstra          | MiBench | M            | ${\rm L}$    | Η        | ${ m L}$     | Multi    | $\operatorname{GPL}$      | network              |

| FDCT              | WCET    | Η            | Η            | ${ m L}$ | $\mathbf{H}$ | Single   | $\mathrm{None}^\dagger$   | consumer             |

| Float Matmult     | WCET    | M            | Η            | M        | ${\bf M}$    | Single   | $\operatorname{GPL}$      | automotive, consumer |

| Integer Matmult   | WCET    | M            | M            | Η        | ${ m L}$     | Single   | $\mathrm{None}^{\dagger}$ | automotive           |

| Rjindael          | MiBench | Η            | $\mathbf{L}$ | M        | ${ m L}$     | Multi    | $\operatorname{GPL}$      | security             |

| SHA               | MiBench | Η            | M            | M        | ${ m L}$     | Multi    | $\operatorname{GPL}$      | network, security    |

| 2D FIR            | WCET    | $\mathbf{H}$ | $\mathbf{M}$ | ${ m L}$ | Η            | Single   | $\mathrm{None}^\dagger$   | automotive, consumer |

# Choosing the Platforms

- Range of different features in the platforms chosen

- Pipeline Depth

- Multi- vs Single- core

- FPU available?

- Caching

- On-chip vs off-chip memory

# Platforms Chosen

| ARM Cortex-M0   | ARM Cortex-M3                                      | ARM Cortex-A8                      | XMOS L1          | Adapteva<br>Epiphany        |

|-----------------|----------------------------------------------------|------------------------------------|------------------|-----------------------------|

| Small memory    | Small memory                                       | Large memory                       | Small memory     | On-chip and off-chip memory |

| Simple Pipeline | Simple Pipeline,<br>with forwarding<br>logic, etc. | Complex<br>superscalar<br>pipeline | Simple pipeline  | Simple superscalar pipeline |

|                 |                                                    | SIMD/FPU                           |                  | FPU                         |

|                 |                                                    |                                    | Multiple threads | 16 cores                    |

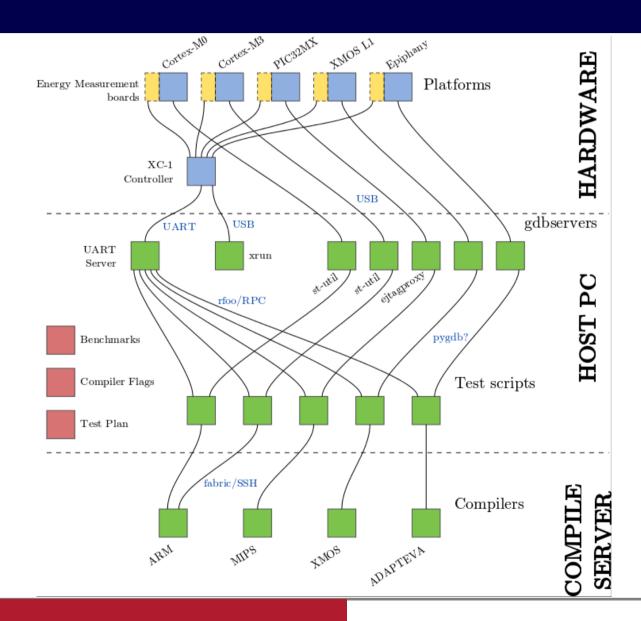

# Experimental Methodology

- Compiler optimizations have many non-linear interactions

- 238 optimization passes combined into 150 different options (GCC)

- 82 compiler options enabled by O3

- How to test all of these, while accounting for the interactions between optimizations?

#### **Fractional Factorial Designs**

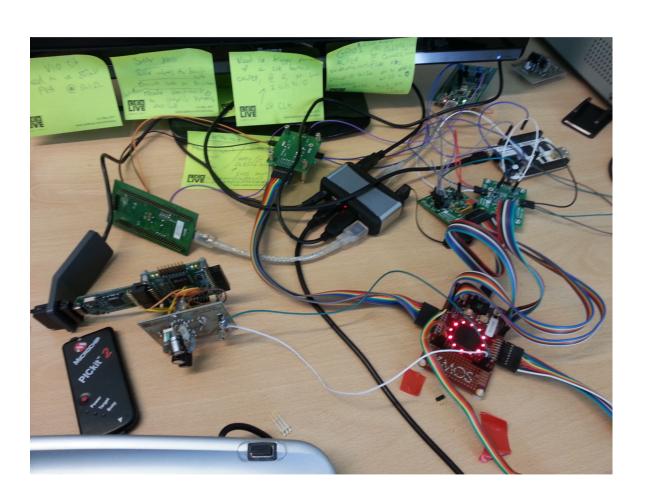

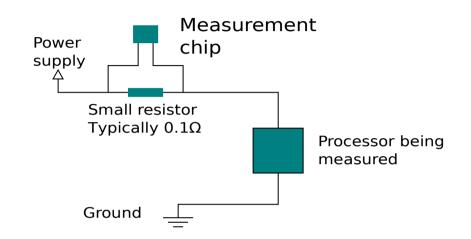

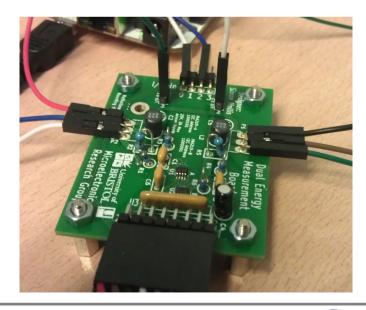

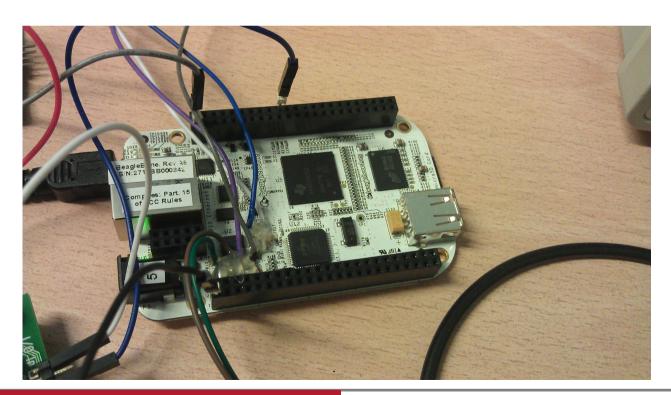

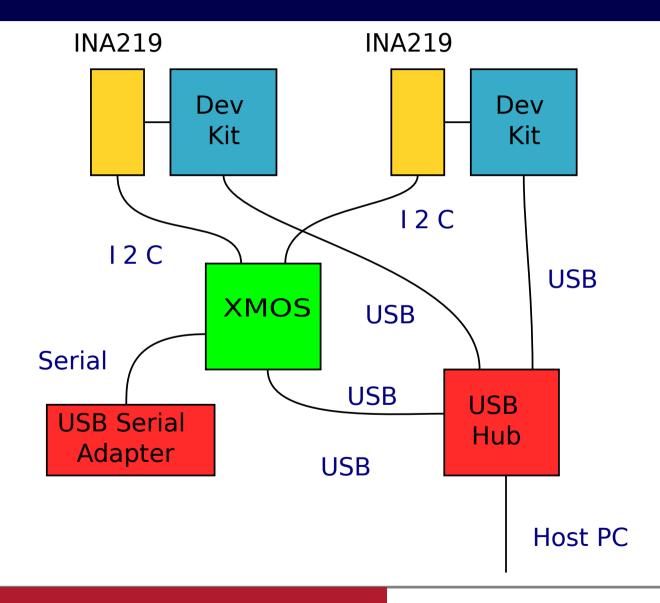

#### Hardware Measurements

- Current, voltage and power monitor

- 10 kSamples/s

- Low noise

- XMOS board to control and timestamp measurements

- Integrate to get energy consumption

# Instrumenting the Hardware

- How to attach the power measurement circuit to the hardware?

- Invasive...

# Hardware

#### Software

#### Results

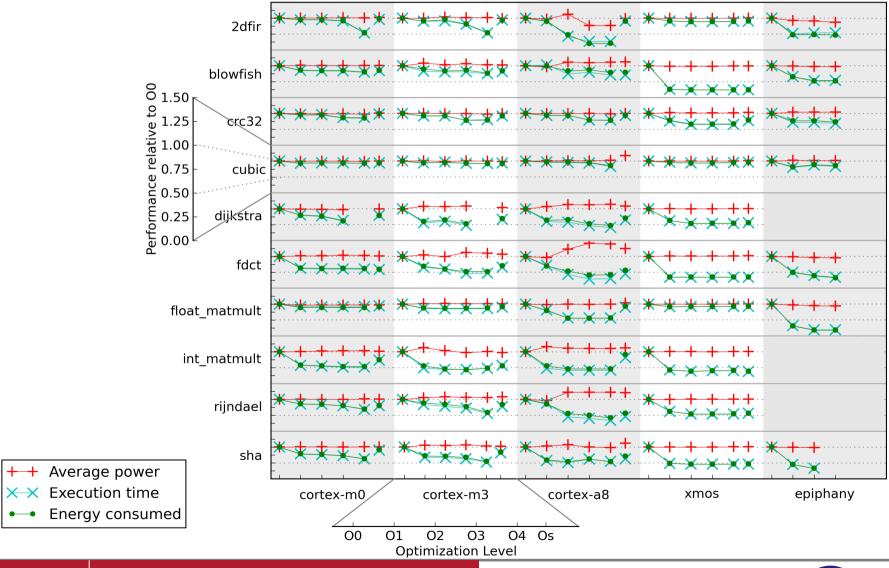

- Energy consumption ≈ Execution time

- Generalization, not true in every case

- Optimization unpredictability

No optimization is universally good across benchmarks and platforms

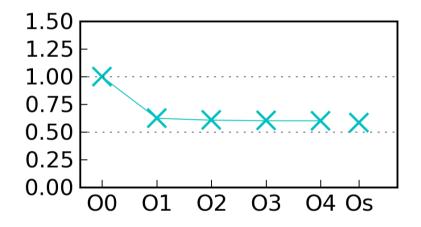

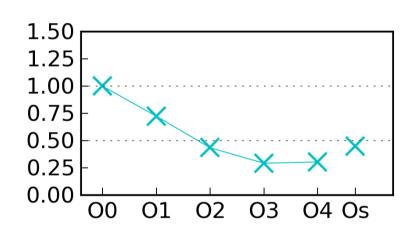

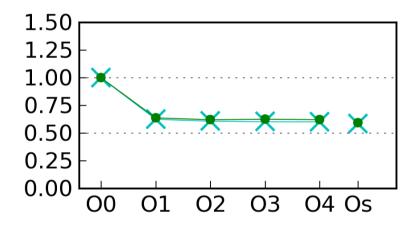

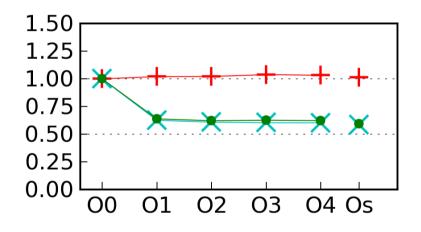

FDCT, Cortex-M0

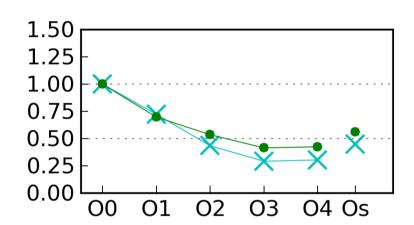

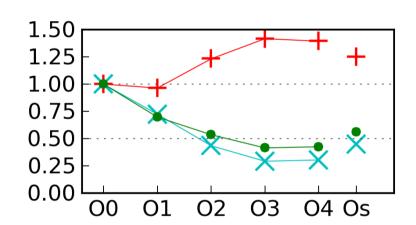

FDCT, Cortex-A8

×× Execution time

FDCT, Cortex-M0

FDCT, Cortex-A8

×× Execution time

Energy consumed

FDCT, Cortex-M0

FDCT, Cortex-A8

++ Average power

×× Execution time

Energy consumed

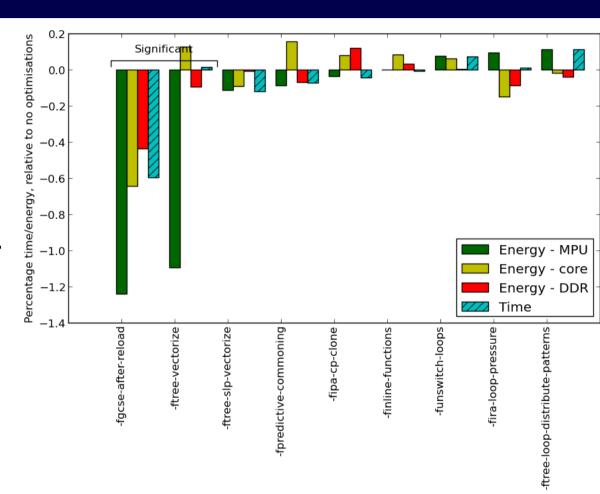

# When Time ≠ Energy

- Complex pipeline

- -ftree-vectorize

- NEON SIMD unit

- Much lower power

O3 Flags, 2DFIR, Cortex-A8

# Conclusion: Mostly, Time ≈ Energy

- Highly correlated

- Especially so for 'simple' pipelines

- Little scope for stalling or superscalar execution

- Complex pipelines:

- Still a correlation

- But more variability

- SIMD, superscalar execution

- To get the most optimal energy consumption we need better than "go fast"

# Case Study: Cortex-M0

#### What does this mean?

#### For the Compiler Writer

- Current optimization levels (O1, O2, etc.) are a good balance between compile time and performance/energy.

- Never completely optimal

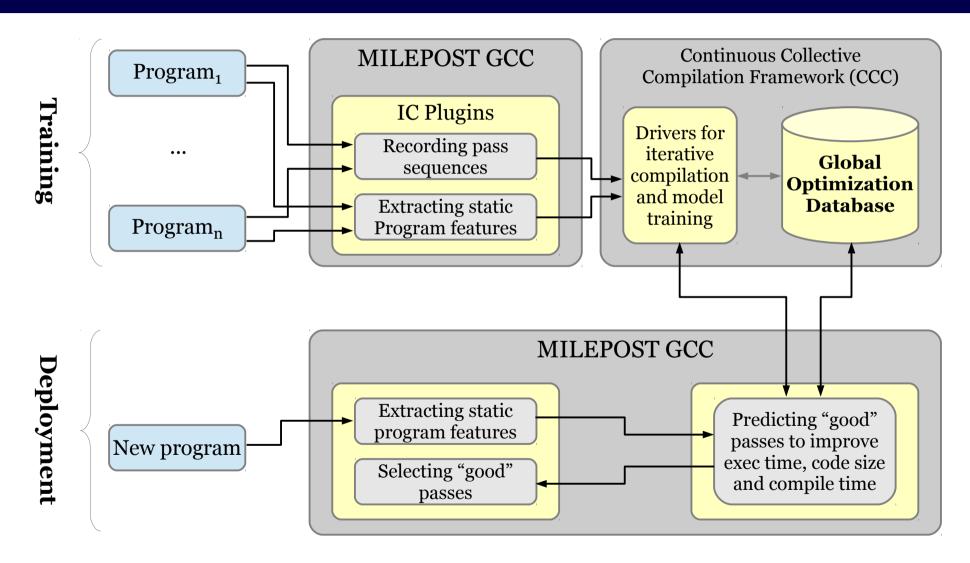

- Machine learning

- MILEPOST

- Genetic algorithms

- Current optimizations targeted for performances

- Few (if any) optimizations in current compilers designed to reduce energy consumption

#### What does this mean?

#### For the embedded developer

- Try the optimization levels – O3 is a good bet

- Use hardware peripherals

- SIMD

- Power Modes

- Sleep

- Memory

- Closer to the processor the better

- Exploit RAM

#### MILEPOST GCC

#### Conclusion

- Time ≈ Energy

- True for simple pipelines

- Mostly true for complex pipelines

- Good approximation

- Optimization unpredictability

- Difficult to model the interactions between optimizations

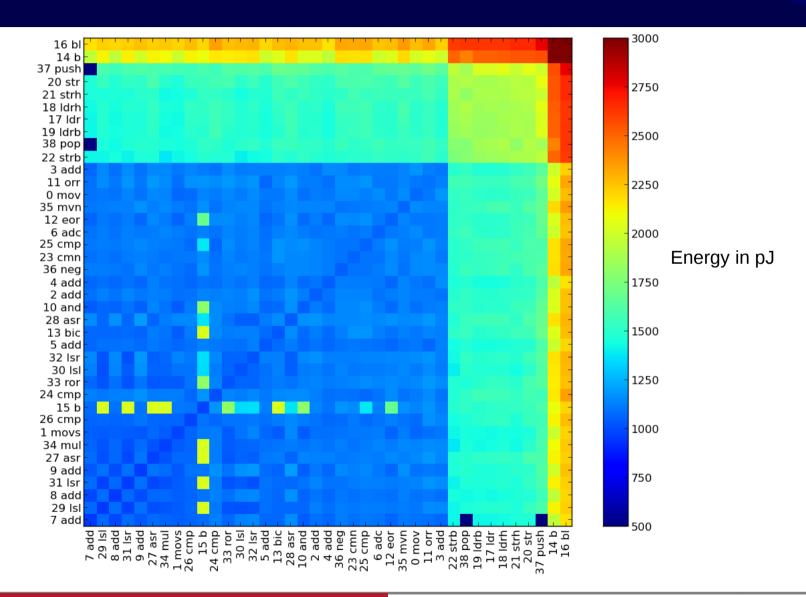

- Commonality across platforms

- Instruction set plays a role

- Common options for the ARM platforms, but not Epiphany

# Questions and Demonstration

james.pallister@bristol.ac.uk simon@cs.bris.ac.uk jeremy.bennett@embecosm.com

All data at: www.jpallister.com/wiki